Najnowsze dociekania serwisu AnandTech rzuciły nowe światło na to, dlaczego procesory AMD mogą mieć problem ze zwiększeniem liczby rdzeni na ten moment. Wszystko najwyraźniej rozbija się o wykorzystaną magistralę.

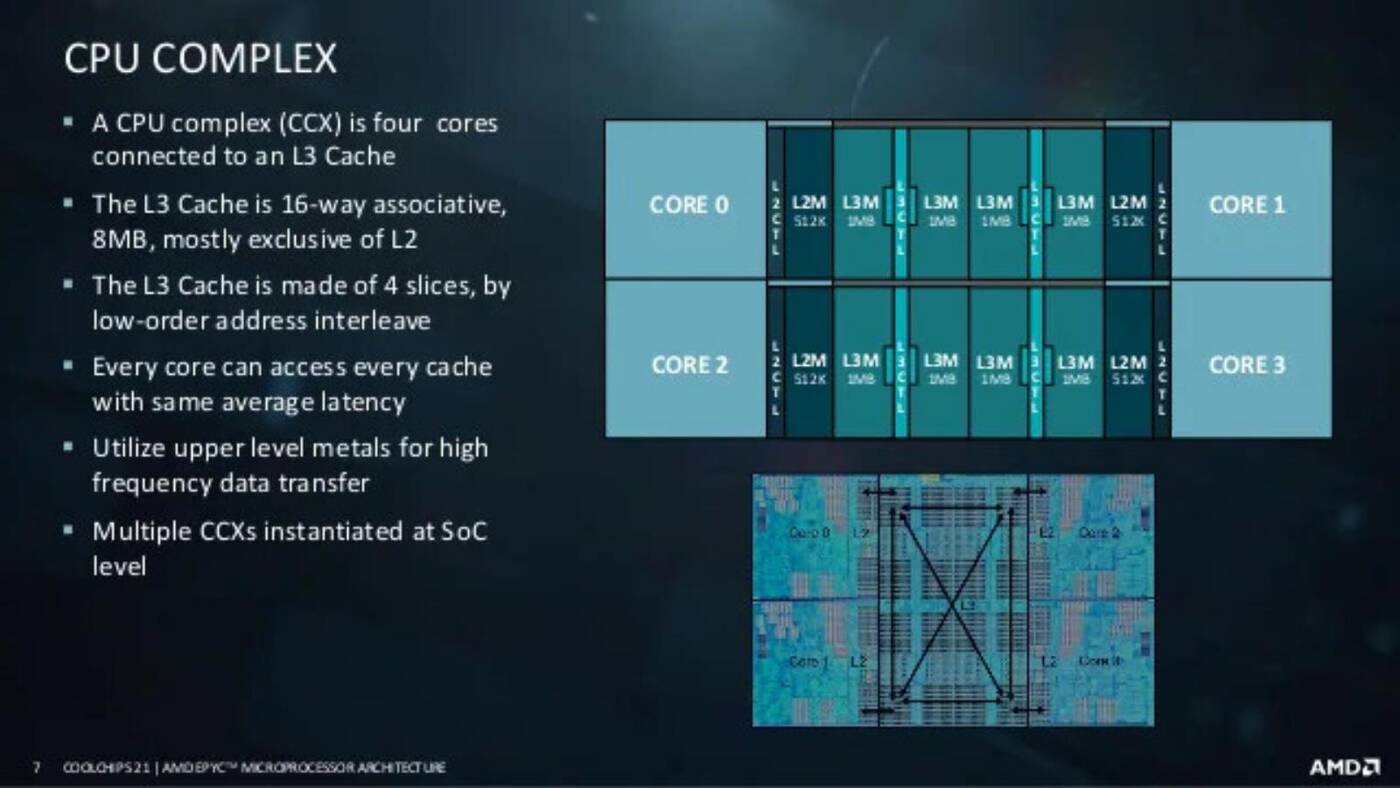

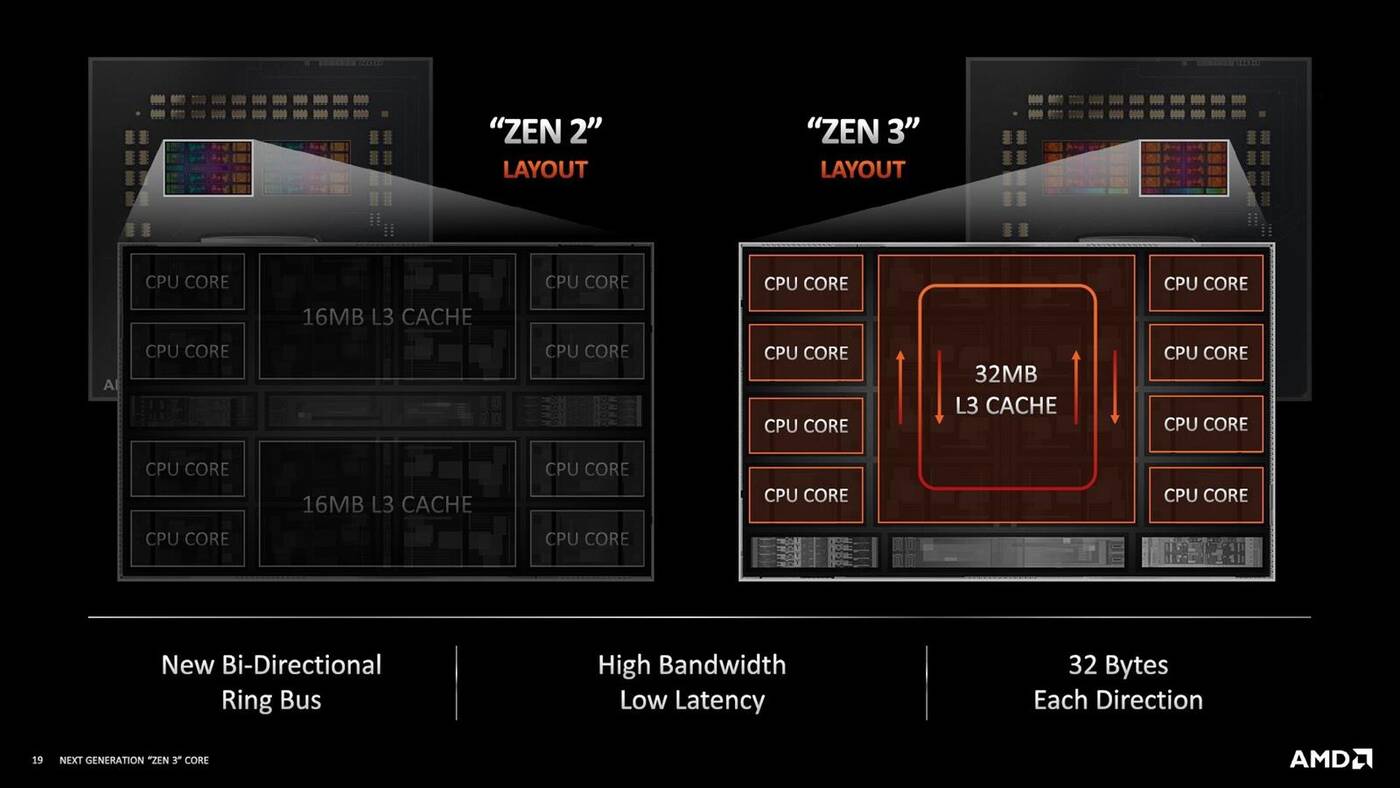

Magistrala, to fizyczne i cyfrowe połączenie między konkretnymi wewnętrznymi elementami (w tym przypadku) procesora. W AMD Ryzen 5000 na bazie architektury Zen 3 znajdują się CCD (Compute Complex Die), czyli specjalnego rodzaju matryce obliczeniowe. To w nich łączy się osiem rdzeni procesora z m.in. 32 MB współdzielonej pamięci cache poziomu trzeciego i interfejsem IFOP z wykorzystaniem dwukierunkowej magistrali pierścieniowej (Bi-Directional Ring Bus).

Czytaj też: AMD pracuje ciągle nad Frontier. To będzie najwydajniejszy superkomputer

To sprawia, że każdy element jest połączony w pewnego rodzaju okręgu, w którym informacje krążą jednocześnie w jednym i drugim kierunku. Nie brzmi to źle, ale w rzeczywistości komunikacja między dwoma najbardziej oddalonymi od siebie elementami wymaga przejścia po „połowie innych” elementów. To z kolei doprowadza do wzrostu opóźnień i dlatego m.in Intel przed 11 laty porzucił tę magistralę na rzecz topologii siatki (Mesh).

Czytaj też: AMD szykuje Radeona RX 6900 XTX do walki z RTX 3090?

Topologia siatki, to to bardziej zaawansowana magistrala pierścieniowa, ale z dodatkowymi bezpośrednimi punktami łączności między komponentami. AMD z kolei zaliczyło małe rendez-vois z jej jeszcze bardziej zaawansowaną wariacją, bo polegającą na bezpośrednim połączeniu wszystkich elementów ze sobą przy procesorach Ryzen Zen 2 z 4-rdzeniowymi blokami CCX. Finalnie w obecnej generacji Ryzenów AMD postawiło na 8-rdzeniowe CCX w formie CCD z wewnętrzną dwukierunkową magistralą pierścieniową.

Czytaj też: Radeony RX 7000 sięgną po rdzenie z RX 6000? AMD zabawi się w recykling

Przechodząc już do konkluzji, wygląda teraz na to, że w przyszłości AMD być może będzie musiało zrezygnować z magistrali pierścieniowej, aby móc zwiększyć liczbę rdzeni procesora na każdy blok CCD.